在现代电子设备中,晶振作为时钟源在电路中发挥着关键作用。随着电子设备的不断小型化,晶振的小型化电路设计变得尤为重要。

本文将为您介绍晶振小型化电路设计的关键要点和技巧,帮助您在紧凑空间中实现高性能的时钟系统。

1. 选取合适的晶振: 在小型化电路设计中,选择适合尺寸和频率范围的晶振至关重要。要考虑晶振的频率稳定性、温度特性和功耗等因素,确保其在小型化环境下能够稳定工作。

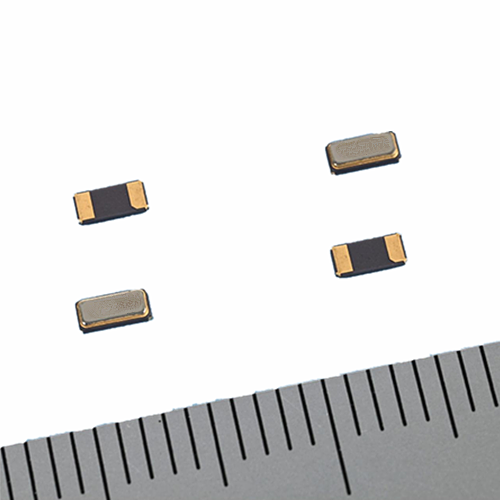

2. 高集成度的封装: 选择高集成度的封装有助于减少电路板上的占用空间。例如,表面贴装封装(SMD)可以显著减小晶振组件的尺寸。

3. 布局和层次设计: 合理的电路布局和层次设计可以减少信号干扰和串扰。将晶振与其他敏感电路分开布局,同时避免信号线交叉,可以提高电路性能。

4. 噪声抑制: 在小型化电路中,噪声抑制尤为重要。采用地线隔离、电磁屏蔽和滤波器等技术,可以有效降低干扰对晶振的影响。

5. 电源稳定性: 晶振对电源稳定性要求较高,尤其是在小型化电路中。确保电源电压的稳定性和纹波小,有助于维持晶振的稳定振荡。

6. 优化引脚布局: 合理的引脚布局可以降低晶振引脚之间的串扰。参考晶振厂家提供的引脚布局建议,尽量减少引脚长度和交叉。

7. 精密校准: 在设计中考虑加入自动校准电路,可以提高晶振的频率稳定性。校准电路可以周期性地校准晶振频率,适应环境变化。

8. 温度补偿: 小型化电路往往更容易受到温度变化的影响。引入温度传感器和自动温度补偿电路,有助于在不同温度下维持晶振的精确频率输出。

在小型化电路设计中,晶振的合理选择和优化设计是确保高性能时钟系统的关键。通过选取合适的晶振、优化布局、抑制噪声等措施,可以实现小型化环境下的稳定工作。为了获得最佳性能,建议结合实际应用需求进行定制化设计。